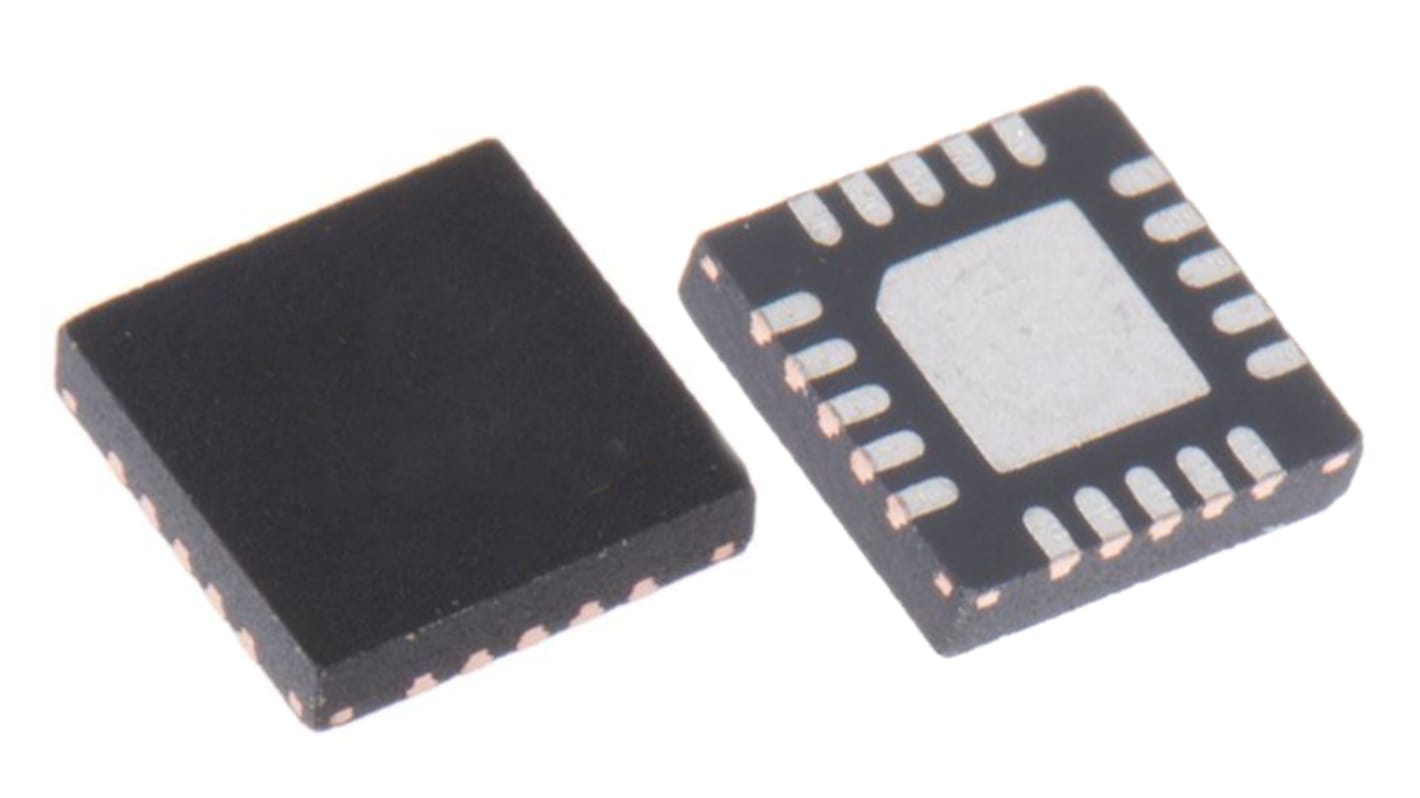

Renesas Electronics 5P49EE502NDGI, PLL Clock Generator 4.6 V 20-Pin VFQFPN

- RS Stock No.:

- 262-8959P

- Mfr. Part No.:

- 5P49EE502NDGI

- Brand:

- Renesas Electronics

Bulk discount available

Subtotal 10 units (supplied in a tray)*

£24.80

(exc. VAT)

£29.80

(inc. VAT)

FREE delivery for orders over £50.00

Temporarily out of stock

- 624 unit(s) shipping from 10 November 2025

Need more? Click ‘Check delivery dates’ to find extra stock and lead times.

Units | Per unit |

|---|---|

| 10 - 48 | £2.48 |

| 50 - 98 | £2.345 |

| 100 - 248 | £2.03 |

| 250 + | £1.92 |

*price indicative

- RS Stock No.:

- 262-8959P

- Mfr. Part No.:

- 5P49EE502NDGI

- Brand:

- Renesas Electronics

Specifications

Technical Reference

Legislation and Compliance

Product Details

Find similar products by selecting one or more attributes.

Select all | Attribute | Value |

|---|---|---|

| Brand | Renesas Electronics | |

| Maximum Output Frequency | 120MHz | |

| Package Type | VFQFPN | |

| Pin Count | 20 | |

| Maximum Operating Supply Voltage | 4.6 V | |

| Select all | ||

|---|---|---|

Brand Renesas Electronics | ||

Maximum Output Frequency 120MHz | ||

Package Type VFQFPN | ||

Pin Count 20 | ||

Maximum Operating Supply Voltage 4.6 V | ||

- COO (Country of Origin):

- TH

The Renesas Electronics Versa clock low power PLL is a programmable clock generator intended for low power, battery operated consumer applications. There are four internal PLLs, each individually programmable, allowing for up to five different output frequencies. The frequencies are generated from a single reference clock. The reference clock can come from either a TCXO or fundamental mode crystal. The versa clock low power PLL can be programmed through the use of the I2C interfaces. The programming interface enables the device to be programmed when it is in normal operation or what is commonly known as in system programmable. An internal EEPROM allows the user to save and restore the configuration of the device without having to reprogram it on power-up.

2 independent adjustable VDDO groups

Programmable slew rate control

Programmable loop bandwidth settings

Programmable output inversion to reduce bimodal jitter

Individual output enable or disable

Power-down or sleep mode 10μA max in power down mode

1.8V VDD Core Voltage

Programmable slew rate control

Programmable loop bandwidth settings

Programmable output inversion to reduce bimodal jitter

Individual output enable or disable

Power-down or sleep mode 10μA max in power down mode

1.8V VDD Core Voltage