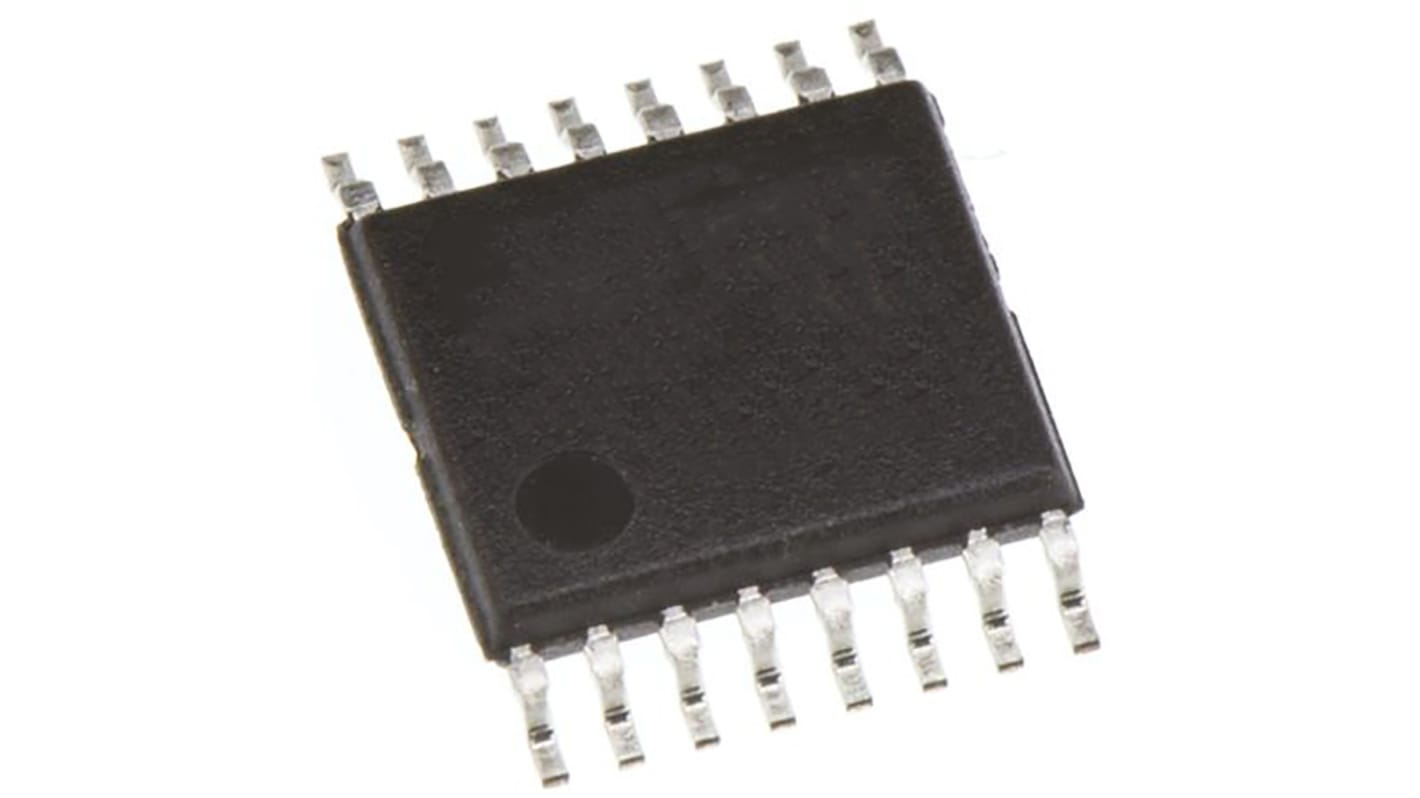

Infineon CY2308ZXI-1H PLL Clock Buffer 16-Pin TSSOP

- RS Stock No.:

- 194-9020P

- Mfr. Part No.:

- CY2308ZXI-1H

- Brand:

- Infineon

Bulk discount available

Subtotal 5 units (supplied in a tube)*

£61.15

(exc. VAT)

£73.40

(inc. VAT)

FREE delivery for orders over £50.00

Last RS stock

- Final 1 unit(s), ready to ship

Units | Per unit |

|---|---|

| 5 - 9 | £12.23 |

| 10 - 24 | £11.97 |

| 25 - 49 | £11.20 |

| 50 + | £10.42 |

*price indicative

- RS Stock No.:

- 194-9020P

- Mfr. Part No.:

- CY2308ZXI-1H

- Brand:

- Infineon

Specifications

Technical Reference

Legislation and Compliance

Product Details

Find similar products by selecting one or more attributes.

Select all | Attribute | Value |

|---|---|---|

| Brand | Infineon | |

| Number of Elements per Chip | 1 | |

| Maximum Supply Current | 70 mA | |

| Maximum Input Frequency | 133.3MHz | |

| Mounting Type | Surface Mount | |

| Package Type | TSSOP | |

| Pin Count | 16 | |

| Dimensions | 5.1 x 4.5 x 0.95mm | |

| Length | 5.1mm | |

| Width | 4.5mm | |

| Height | 0.95mm | |

| Maximum Operating Supply Voltage | 3.6 V | |

| Maximum Operating Temperature | +85 °C | |

| Maximum Output Frequency | 133.3MHz | |

| Minimum Operating Supply Voltage | 3 V | |

| Minimum Output Frequency | 10MHz | |

| Minimum Operating Temperature | -40 °C | |

| Select all | ||

|---|---|---|

Brand Infineon | ||

Number of Elements per Chip 1 | ||

Maximum Supply Current 70 mA | ||

Maximum Input Frequency 133.3MHz | ||

Mounting Type Surface Mount | ||

Package Type TSSOP | ||

Pin Count 16 | ||

Dimensions 5.1 x 4.5 x 0.95mm | ||

Length 5.1mm | ||

Width 4.5mm | ||

Height 0.95mm | ||

Maximum Operating Supply Voltage 3.6 V | ||

Maximum Operating Temperature +85 °C | ||

Maximum Output Frequency 133.3MHz | ||

Minimum Operating Supply Voltage 3 V | ||

Minimum Output Frequency 10MHz | ||

Minimum Operating Temperature -40 °C | ||

The CY2308 is a 3.3 V Zero Delay Buffer designed to distribute high speed clocks in PC, workstation, datacom, telecom, and other high performance applications. The part has an on-chip PLL that locks to an input clock presented on the REF pin. The PLL feedback is driven from external FBK pin, so user has flexibility to choose any one of the outputs as feedback input and connect it to FBK pin. The input-to-output skew is less than 250 ps and output-to-output skew is less than 200 ps. The CY2308 has two banks of four outputs each that is controlled by the select inputs as shown in the table Select Input Decoding on page 3. If all output clocks are not required, Bank B is three-stated. The input clock is directly applied to the output for chip and system testing purposes by the select inputs. The CY2308 PLL enters a power down state when there are no rising edges on the REF input. In this mode, all outputs are three-stated and the PLL is turned off resulting in less than 25 μA of current draw.