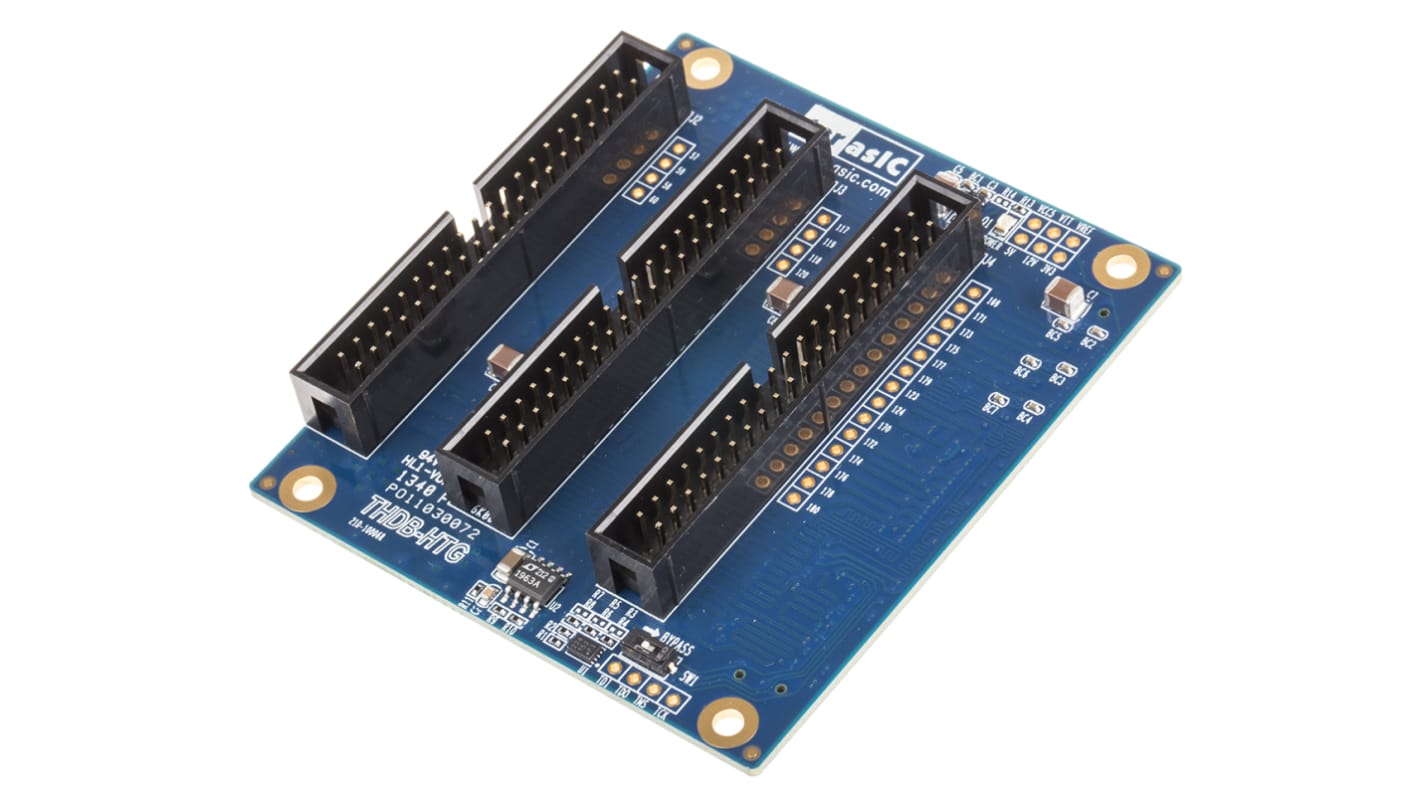

Terasic GPIO to HSMC/HSTC Adapter Board P0024

- RS Stock No.:

- 768-9048

- Mfr. Part No.:

- P0024

- Brand:

- Terasic

Price Each

£53.87

(exc. VAT)

£64.64

(inc. VAT)

1 In stock - FREE next working day delivery available*

* Delivery dates may change based on your chosen quantity and delivery address.

Units | Per unit |

|---|---|

| 1 - 4 | £53.87 |

| 5 - 9 | £52.49 |

| 10 + | £51.18 |

- RS Stock No.:

- 768-9048

- Mfr. Part No.:

- P0024

- Brand:

- Terasic

Related links

- Terasic SDI to HSMC Adapter Board P0039

- Texas Instruments EM Adapter Board CCEMADAPTER Adapter Board for...

- Okdo WIFI and Bluetooth Interface Adapter Board Bluetooth Module,...

- MikroElektronika Monarch Adapter Click 541670208 Adapter Board for...

- STMicroelectronics Voltage adapter board for STLINK-V3SET...

- Parallax Inc XBee USB RF Transceiver Adapter Board for XBee Modules 32400

- MikroElektronika Dot Matrix R Click HCMS-3906 Adapter Board for...

- MikroElektronika M-Bus Slave Click TSS721A Adapter Board for...