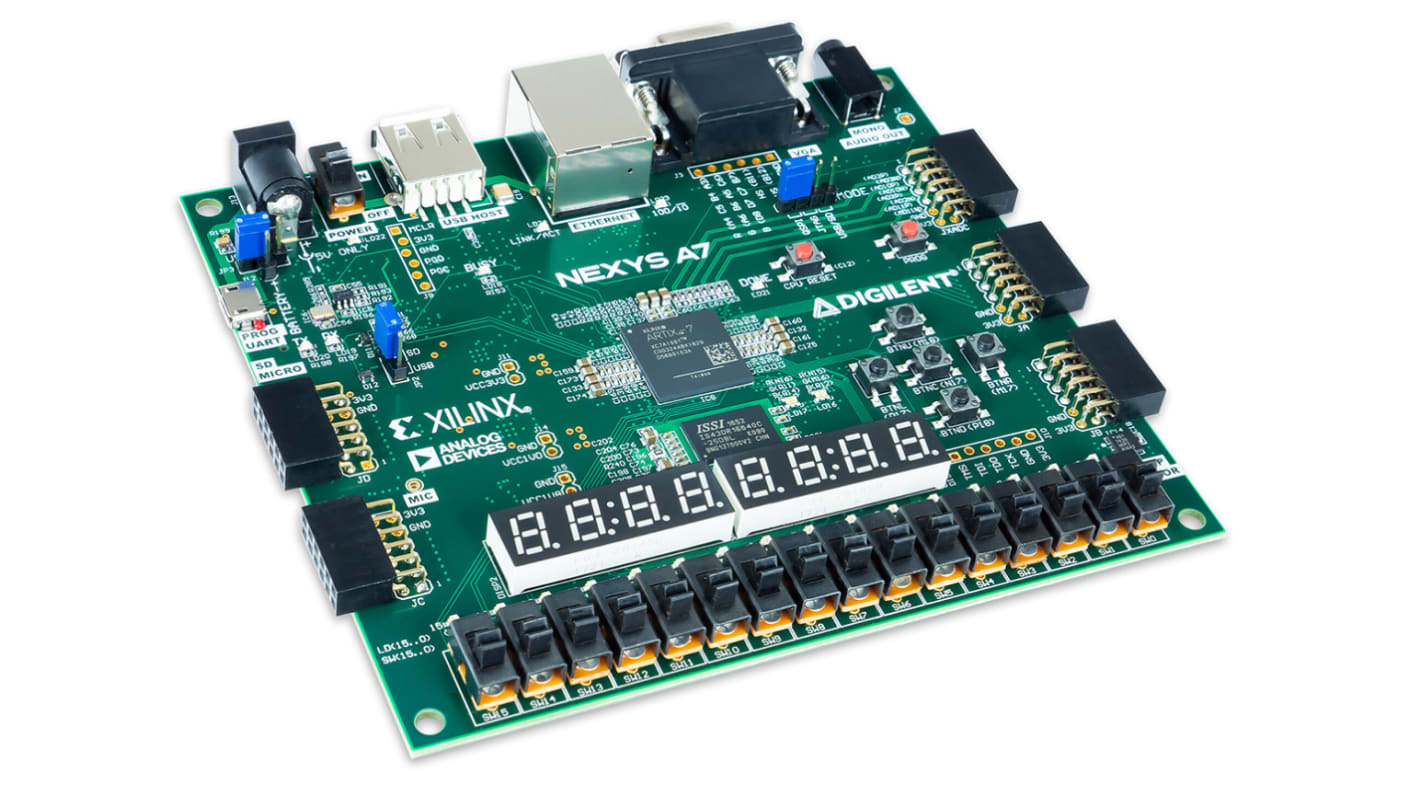

Digilent 410-292-1 to Nexys A7-50T FPGA Trainer Board Recommended for ECE Curriculum Development Board for Nexys 4 DDR

- RS Stock No.:

- 193-2597

- Mfr. Part No.:

- 410-292-1 to Nexys A7-50T

- Brand:

- Digilent

Unavailable

RS will no longer stock this product.

- RS Stock No.:

- 193-2597

- Mfr. Part No.:

- 410-292-1 to Nexys A7-50T

- Brand:

- Digilent

Specifications

Technical Reference

Legislation and Compliance

Product Details

Find similar products by selecting one or more attributes.

Select all | Attribute | Value |

|---|---|---|

| Brand | Digilent | |

| Programmable Logic Technology | FPGA | |

| Classification | Trainer Board | |

| Kit Classification | Development Board | |

| For Use With | Nexys 4 DDR Board | |

| Kit Name | FPGA Trainer Board Recommended for ECE Curriculum | |

| Select all | ||

|---|---|---|

Brand Digilent | ||

Programmable Logic Technology FPGA | ||

Classification Trainer Board | ||

Kit Classification Development Board | ||

For Use With Nexys 4 DDR Board | ||

Kit Name FPGA Trainer Board Recommended for ECE Curriculum | ||

- COO (Country of Origin):

- TW

Xilinx Artix-7 FPGA XC7A100T-1CSG324C or XC7A50T-1CSG324C

15,850 logic slices, each with four 6-input LUTs and 8 flip-flops (8,150 logic slices for the A7-50T)

4,860 Kbits of fast block RAM (2,700 Kbits for the A7-50T)

Six clock management tiles, each with phase-locked loop (PLL) (5 clock management tiles for the A7-50T)

240 DSP slices (120 DSP slices for A7-50T)

Internal clock speeds exceeding 450 MHz

On-chip analog-to-digital converter (XADC)

128 MB DDR2

Serial Flash

Digilent USB-JTAG port for FPGA programming and communication

microSD card connector

Ships with rugged plastic case and USB cable

USB-UART Bridge

10/100 Ethernet PHY

PWM audio output

3-axis accelerometer

16 user switches

16 user LEDs

Two tri-color LEDs

PDM microphone

Temperature sensor

Two 4-digit 7-segment displays

USB HID Host for mice, keyboards and memory sticks

Pmod for XADC signals

12-bit VGA output

Four Pmod ports

15,850 logic slices, each with four 6-input LUTs and 8 flip-flops (8,150 logic slices for the A7-50T)

4,860 Kbits of fast block RAM (2,700 Kbits for the A7-50T)

Six clock management tiles, each with phase-locked loop (PLL) (5 clock management tiles for the A7-50T)

240 DSP slices (120 DSP slices for A7-50T)

Internal clock speeds exceeding 450 MHz

On-chip analog-to-digital converter (XADC)

128 MB DDR2

Serial Flash

Digilent USB-JTAG port for FPGA programming and communication

microSD card connector

Ships with rugged plastic case and USB cable

USB-UART Bridge

10/100 Ethernet PHY

PWM audio output

3-axis accelerometer

16 user switches

16 user LEDs

Two tri-color LEDs

PDM microphone

Temperature sensor

Two 4-digit 7-segment displays

USB HID Host for mice, keyboards and memory sticks

Pmod for XADC signals

12-bit VGA output

Four Pmod ports